Компания Applied Materials представила новый способ выполнения внутренних соединений в логических микросхемах, который позволяет масштабировать их до норм 3 нм и далее.

При освоении всё более тонких норм уменьшение размеров улучшает характеристики транзистора, но увеличивает сопротивление внутренних соединений, поскольку оно обратно пропорционально их сечению. Это снижает производительность и увеличивает энергопотребление микросхем. Без прорыва в области материаловедения, сопротивление внутренних соединений при переходе от норм 7 нм к нормам 3 нм увеличилось бы в 10 раз, сводя на нет преимущества масштабирования транзисторов.

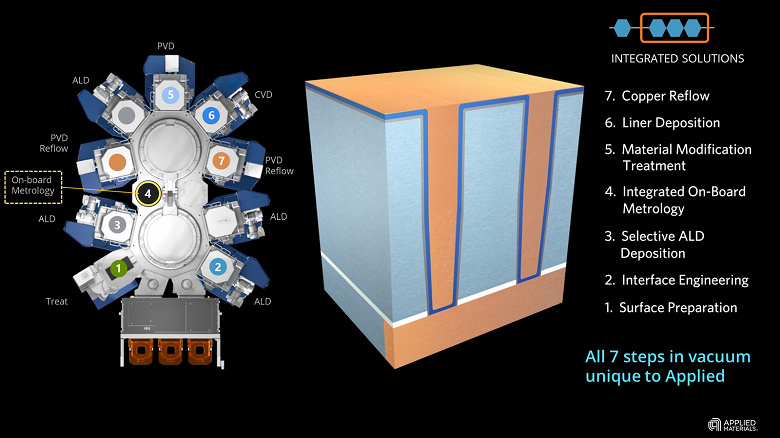

Чтобы исправить ситуацию, компания Applied Materials разработала интегрированное производственное решение под названием Endura Copper Barrier Seed IMS. В нём в одной системе в условиях высокого вакуума выполняются семь различных технологических процессов: подготовка поверхности, модификация поверхности на атомном уровне, выборочное атомно-слоевое осаждение (ALD), метрологический контроль, вакуумное напыление (PVD), химическое осаждение из газовой фазы (CVD) и оплавление меди. Применение выборочного ALD вместо конформного устраняет барьер с высоким удельным сопротивлением. Решение также включает этап оплавления меди, на котором узкие зазоры заполняются за счет капиллярного эффекта. Как утверждается, уменьшение сопротивления сквозных контактов за счёт применения новой технологии достигает 50%.

Остаётся добавить, что система Endura Copper Barrier Seed IMS уже используется ведущими заказчиками Applied Materials.